Menu

Operating System GATE Question Answers with Explanation.

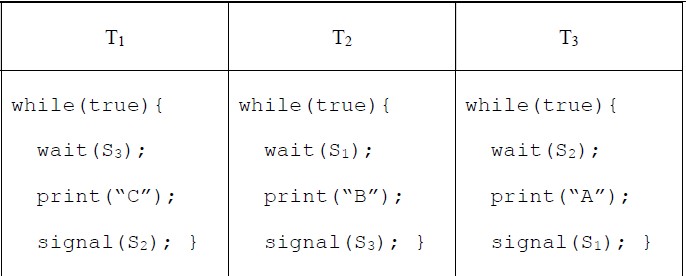

Q1 – Consider the following threads, T1, T2, and T3 executing on a single processor, synchronized using three binary semaphore variables, S1, S2, and S3, operated upon using standard wait() and signal(). The threads can be context switched in any order and at any time.

Which initialization of the semaphores would print the sequence BCABCABCA….? (GATE 2022)

S1 = 1; S2 = 1; S3 = 1

S1 = 1; S2 = 1; S3 = 0

S1 = 1; S2 = 0; S3 = 0

S1 = 0; S2 = 1; S3 = 1

Ans – (3)

Explanation –

Q2 – Let WB and WT be two set associative cache organizations that use LRU algorithm for cache block replacement. WB is a write back cache and WT is a write through cache. Which of the following statements is/are FALSE? (GATE 2022)

Each cache block in WB and WT has a dirty bit.

Every write hit in WB leads to a data transfer from cache to main memory.

Eviction of a block from WT will not lead to data transfer from cache to main memory.

A read miss in WB will never lead to eviction of a dirty block from WB.

Ans – (1, 2, 4)

Explanation –

Q3 – A cache memory that has a hit rate of 0.8 has an access latency 10 ns and miss penalty 100 ns. An optimization is done on the cache to reduce the miss rate. However, the optimization results in an increase of cache access latency to 15 ns, whereas the miss penalty is not affected. The minimum hit rate (rounded off to two decimal places) needed after the optimization such that it should not increase the average memory access time is _____________. (GATE 2022)

Ans – (0.85)

Explanation –

Q4 – Which one of the following statements is FALSE?

The TLB performs an associative search in parallel on all its valid entries using page number of incoming virtual address.

If the virtual address of a word given by CPU has a TLB hit, but the subsequent search for the word results in a cache miss, then the word will always be present in the main memory.

The memory access time using a given inverted page table is always same for all incoming virtual addresses.

In a system that uses hashed page tables, if two distinct virtual addresses V1 and V2 map to the same value while hashing, then the memory access time of these addresses will not be the same. (GATE 2022)

Ans – (3)

Explanation –

Q5 – Consider four processes P, Q, R, and S scheduled on a CPU as per round robin algorithm with a time quantum of 4 units. The processes arrive in the order P, Q, R, S, all at time t = 0. There is exactly one context switch from S to Q, exactly one context switch from R to Q, and exactly two context switches from Q to R. There is no context switch from S to P. Switching to a ready process after the termination of another process is also considered a context switch. Which one of the following is NOT possible as CPU burst time (in time units) of these processes? (GATE 2022)

P = 4, Q = 10, R = 6, S = 2

P = 2, Q = 9, R = 5, S = 1

P = 4, Q = 12, R = 5, S = 4

P = 3, Q = 7, R = 7, S = 3

Ans – (4)

Explanation –

Q6 – Consider a system with 2 KB direct mapped data cache with a block size of 64 bytes. The system has a physical address space of 64 KB and a word length of 16 bits.

During the execution of a program, four data words P, Q, R, and S are accessed in that order 10 times (i.e., PQRSPQRS…). Hence, there are 40 accesses to data cache altogether. Assume that the data cache is initially empty and no other data words are accessed by the program. The addresses of the first bytes of P, Q, R, and S are 0xA248, 0xC28A, 0xCA8A, and 0xA262, respectively. For the execution of the above program, which of the following statements is/are TRUE with respect to the data cache? (GATE 2022)

Every access to S is a hit.

Once P is brought to the cache it is never evicted.

At the end of the execution only R and S reside in the cache.

Every access to R evicts Q from the cache.

Ans – (1, 2, 4)

Explanation –