Digital Logic GATE Question Answers with Explanation.

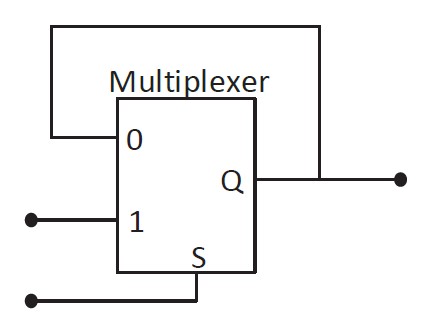

Q1 – The output of a 2-input multiplexer is connected back to one of its inputs as shown in the figure.

Match the functional equivalence of this circuit to one of the following options. (GATE 2023)

D Flip-flop

D Latch

Half-adder

Demultiplexer

Ans – (2)

Explanation – The circuit described, where the output of a 2-input multiplexer is connected back to one of its inputs, is functionally equivalent to a D latch.

In a D latch, one input (typically labeled D for “data”) controls the output state of the latch. When the latch enable input (usually denoted as E or LE) is high, the current value of the D input is latched onto the output.

The scenario described with the multiplexer looping its output back to one of its inputs effectively creates a feedback loop, which is a characteristic feature of a D latch. When properly configured, this feedback loop allows the latch to store and retain its output state, making it suitable for memory storage applications. Therefore, the correct functional equivalence for this circuit is a D latch.

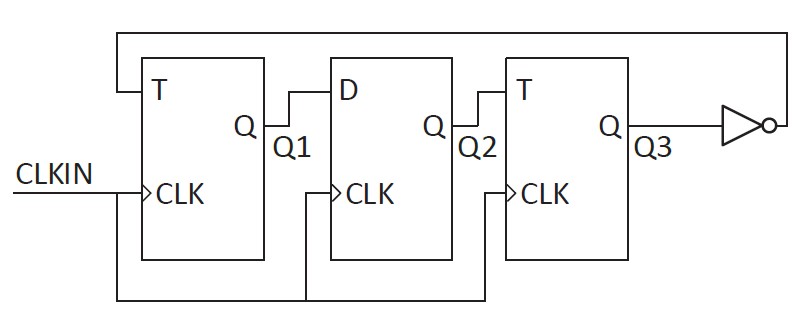

Q2 – Consider a sequential digital circuit consisting of T flip-flops and D flip-flops as shown in the figure. CLKIN is the clock input to the circuit. At the beginning, Q1, Q2 and Q3 have values 0, 1 and 1, respectively.

Which one of the given values of (Q1, Q2, Q3) can NEVER be obtained with this digital circuit? (GATE 2023)

(0, 0, 1)

(1, 0, 0)

(1, 0, 1)

(1, 1, 1)

Ans – (1)

Explanation –

T = Q3′

D = Q1

T = Q2, The next input sequence is as follows

| Initial State | Current Input | Next State | ||||||

| Q1 | Q2 | Q3 | T | D | T | Q1 | Q2 | Q3 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

So (0, 0, 1) value can never be obtained with this digital circuit.

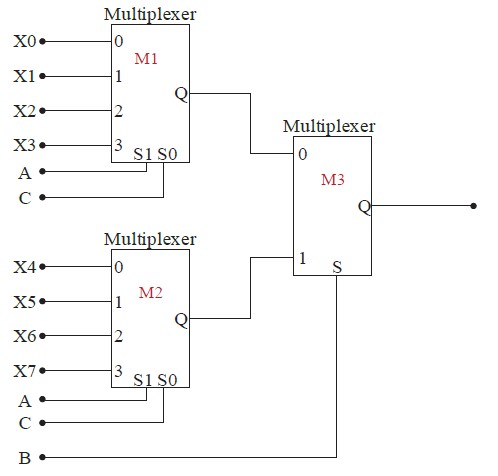

Q3 – A Boolean digital circuit is composed using two 4-input multiplexers (M1 and M2) and one 2-input multiplexer (M3) as shown in the figure. X0–X7 are the inputs of the multiplexers M1 and M2 and could be connected to either 0 or 1. The select lines of the multiplexers are connected to Boolean variables A, B and C as shown.

Which one of the following set of values of (X0, X1, X2, X3, X4, X5, X6, X7) will realise the Boolean function A’ + A’.C’ + A.B’.C? (GATE 2023)

(1, 1, 0, 0, 1, 1, 1, 0)

(1, 1, 0, 0, 1, 1, 0, 1)

(1, 1, 0, 1, 1, 1, 0, 0)

(0, 0, 1, 1, 0, 1, 1, 1)

Ans – (3)

Explanation –

Q4 – Consider the IEEE-754 single precision floating point numbers

P=0xC1800000 and Q=0x3F5C2EF4.

Which one of the following corresponds to the product of these numbers (i.e., P × Q), represented in the IEEE-754 single precision format? (GATE 2023)

0x404C2EF4

0x405C2EF4

0xC15C2EF4

0xC14C2EF4

Ans – (3)

Explanation –