Menu

Computer Architecture & Organization GATE Question Answers with Explanation.

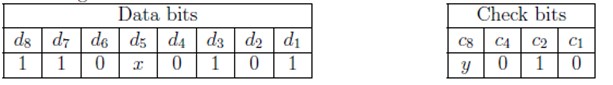

Q1 – Assume that a 12-bit Hamming codeword consisting of 8-bit data and 4 check bits is d8d7d6d5c8d4d4d3d2c4d1c2c1, where the data bits and the check bits are given in the following tables:

Which one of the following choices gives the correct values of x and y? (GATE 2021 SET 1)

x is 0 and y is 0

x is 0 and y is 1

x is 1 and y is 0

x is 1 and y is 1

Ans – (1)

Explanation –

Q2 – Consider the sliding window flow-control protocol operating between a sender and a receiver over a full-duplex error-free link. Assume the following:

The time taken for processing the data frame by the receiver is negligible.

The time taken for processing the acknowledgement frame by the sender is negligible.

The sender has infinite number of frames available for transmission.

The size of the data frame is 2,000 bits and the size of the acknowledgement frame is 10 bits.

The link data rate in each direction is 1 Mbps (= 106 bits per second).

One way propagation delay of the link is 100 milliseconds.

The minimum value of the sender’s window size in terms of the number of frames, (rounded to the nearest integer) needed to achieve a link utilization of 50% is_____________. (GATE 2021 SET 1)

Ans – (50 to 52)

Explanation –

Q3 – A five-stage pipeline has stage delays of 150,120,150,160 and 140 nanoseconds. The registers that are used between the pipeline stages have a delay of 5 nanoseconds each. The total time to execute 100 independent instructions on this pipeline, assuming there are no pipeline stalls, is _______ nanoseconds. (GATE 2021 SET 1)

Ans – (17160)

Explanation –

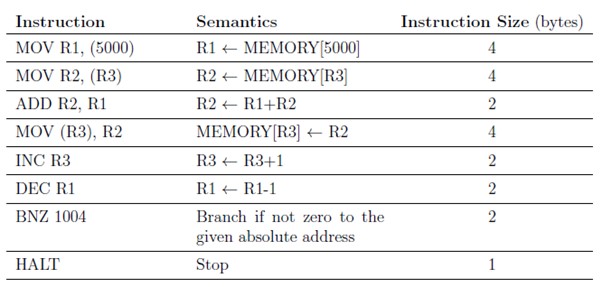

Q4 – Consider the following instruction sequence where registers R1, R2 and R3 are general purpose and MEMORY[X] denotes the content at the memory location X.

Assume that the content of the memory location 5000 is 10, and the content of the register R3 is 3000. The content of each of the memory locations from 3000 to 3010 is 50. The instruction sequence starts from the memory location 1000. All the numbers are in decimal format. Assume that the memory is byte addressable.

After the execution of the program, the content of memory location 3010 is ____________. (GATE 2021 SET 1)

Ans – (50)

Explanation –