Menu

Computer Architecture & Organization GATE Question Answers with Explanation.

Q1 – Consider a 3-stage pipelined processor having a delay of 10 ns (nanoseconds), 20 ns, and 14 ns, for the first, second, and the third stages, respectively. Assume that there is no other delay and the processor does not suffer from any pipeline hazards. Also assume that one instruction is fetched every cycle.

The total execution time for executing 100 instructions on this processor is _________ ns. (GATE 2023)

Ans – (2040)

Explanation –

Q2 – A keyboard connected to a computer is used at a rate of 1 keystroke per second. The computer system polls the keyboard every 10 ms (milli seconds) to check for a keystroke and consumes 100 μs (micro seconds) for each poll. If it is determined after polling that a key has been pressed, the system consumes an additional 200 μs to process the keystroke. Let T1 denote the fraction of a second spent in polling and processing a keystroke.

In an alternative implementation, the system uses interrupts instead of polling. An interrupt is raised for every keystroke. It takes a total of 1 ms for servicing an interrupt and processing a keystroke. Let T2 denote the fraction of a second spent in servicing the interrupt and processing a keystroke.

The ratio T1/T2 is ______. (Rounded off to one decimal place) (GATE 2023)

Ans – (10.2)

Explanation –

Q3 – Consider the given C-code and its corresponding assembly code, with a few operands U1–U4 being unknown. Some useful information as well as the semantics of each unique assembly instruction is annotated as inline comments in the code.

The memory is byte-addressable.

//C-code

int a[10], b[10], i;

// int is 32-bit

for (i=0; i<10; i++)

a[i] = b[i] * 8;

;assembly-code (; indicates comments)

;r1-r5 are 32-bit integer registers

;initialize r1=0, r2=10

;initialize r3, r4 with base address of a, b

L01: jeq r1, r2, end ;if(r1==r2) goto end

L02: lw r5, 0(r4) ;r5 <- Memory[r4+0]

L03: shl r5, r5, U1 ;r5 <- r5 << U1

L04: sw r5, 0(r3) ;Memory[r3+0] <- r5

L05: add r3, r3, U2 ;r3 <- r3+U2

L06: add r4, r4, U3

L07: add r1, r1, 1

L08: jmp U4 ;goto U4

L09: end

Which one of the following options is a CORRECT replacement for operands in the position (U1, U2, U3, U4) in the above assembly code? (GATE 2023)

(8, 4, 1, L02)

(3, 4, 4, L01)

(8, 1, 1, L02)

(3, 1, 1, L01)

Ans – (2)

Explanation –

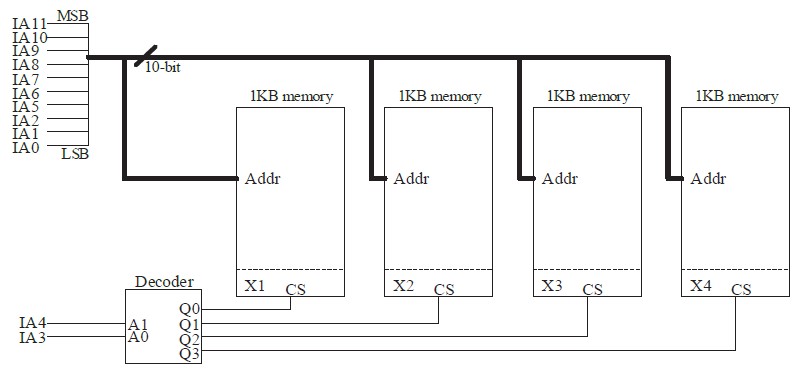

Q4 – A 4 kilobyte (KB) byte-addressable memory is realized using four 1 KB memory blocks. Two input address lines (IA4 and IA3) are connected to the chip select (CS) port of these memory blocks through a decoder as shown in the figure. The remaining ten input address lines from IA11–IA0 are connected to the address port of these blocks. The chip select (CS) is active high.

The input memory addresses (IA11–IA0), in decimal, for the starting locations (Addr=0) of each block (indicated as X1, X2, X3, X4 in the figure) are among the options given below. Which one of the following options is CORRECT? (GATE 2023)

(0, 1, 2, 3)

(0, 1024, 2048, 3072)

(0, 8, 16, 24)

(0, 0, 0, 0)

Ans – (3)

Explanation –

Q5 – An 8-way set associative cache of size 64 KB (1 KB = 1024 bytes) is used in a system with 32-bit address. The address is sub-divided into TAG, INDEX, and BLOCK OFFSET.

The number of bits in the TAG is __________. (GATE 2023)

Ans – (19)

Explanation –